кё°мӮ¬ мӣҗл¬ё -В

https://www.tomshardware.com/news/samsung-to-start-making-3nm-chips-in-q2-2022гҖҖ

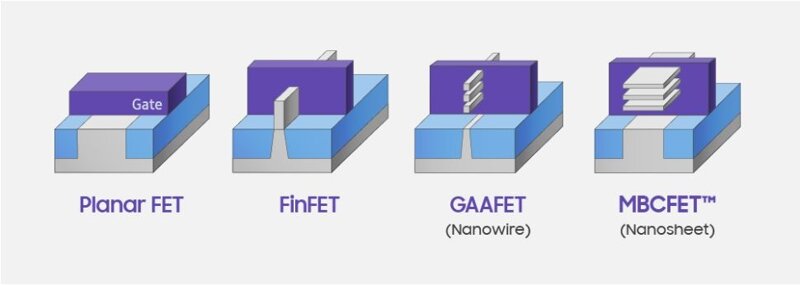

мӮјм„ұ(Samsung)мқҖ 3GAE (3nmкёү кІҢмқҙнҠё л§ҢлҠҘ мЎ°кё°) м ңмЎ° кіөм •мқ„ мӮ¬мҡ©н•ҳм—¬ мқҙлІҲ 분기м—җ лҢҖлҹү мғқмӮ°мқ„ мӢңмһ‘н• мҳҲм •мқҙлқјкі л°қнҳ”мҠөлӢҲлӢӨ. мқҙлІҲ л°ңн‘ңлҠ” м—…кі„ мөңмҙҲмқҳ 3nmкёү м ңмЎ° кё°мҲ мқј лҝҗл§Ң м•„лӢҲлқј GAAFET(кІҢмқҙнҠё л§ҢлҠҘ м „кі„ нҡЁкіј нҠёлһңм§ҖмҠӨн„°)лҘј мӮ¬мҡ©н•ҳлҠ” мөңмҙҲмқҳ л…ёл“ңмқҙкё°лҸ„ н•©лӢҲлӢӨ.

мӮјм„ұмқҳ м„ұлӘ…м„ң[PDF] лҠ” "м„ёкі„ мөңмҙҲмқҳ GAA 3лӮҳл…ё кіөм • м–‘мӮ°мқ„ нҶөн•ҙ кё°мҲ лҰ¬лҚ”мӢӯмқ„ к°•нҷ”н•ңлӢӨ"лқјкі л°қнҳ”мҠөлӢҲлӢӨ.

мӮјм„ұ нҢҢмҡҙл“ңлҰ¬мқҳВ 3GAE кіөм • кё°мҲ В мқҖ мӮјм„ұмқҙ кіөмӢқм ҒмңјлЎң лӢӨмӨ‘ лёҢлҰ¬м§Җ мұ„л„җ м „кі„ нҡЁкіј нҠёлһңм§ҖмҠӨн„°(MBCFET)лқјкі л¶ҖлҘҙлҠ” GAA нҠёлһңм§ҖмҠӨн„°лҘј мӮ¬мҡ©н•ҳлҠ” нҡҢмӮ¬мқҳ мІ« лІҲм§ё кіөм •мһ…лӢҲлӢӨ.

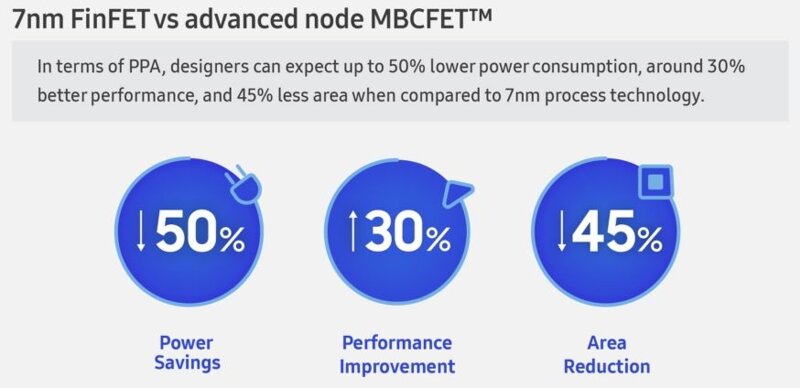

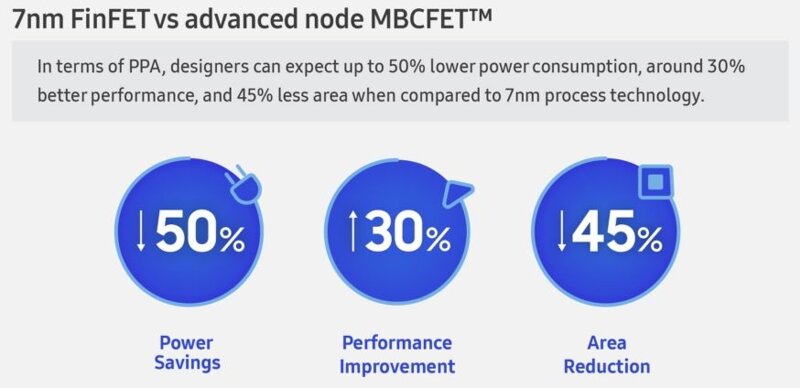

мӮјм„ұмқҖ м•Ҫ 3л…„ м „м—җ 3GAE л°Ҹ 3GAP л…ёл“ңлҘј кіөмӢқм ҒмңјлЎң лҸ„мһ…н–ҲмҠөлӢҲлӢӨ. нҡҢмӮ¬лҠ” 3GAE кё°мҲ мқ„ мӮ¬мҡ©н•ҳм—¬ мғқмӮ°лҗң 256Mb GAAFET SRAM 칩мқ„ м„ӨлӘ…н•ҳл©ҙм„ң м—¬лҹ¬ мЈјмһҘмқ„ нҺјміӨмҠөлӢҲлӢӨ. мӮјм„ұмқҖ мқҙ н”„лЎңм„ёмҠӨлҘј нҶөн•ҙ 30%мқҳ м„ұлҠҘ н–ҘмғҒ, 50%мқҳ м „л Ҙ мҶҢ비 к°җмҶҢ, мөңлҢҖ 80% лҚ” лҶ’мқҖ нҠёлһңм§ҖмҠӨн„° л°ҖлҸ„(лЎңм§Ғ л°Ҹ SRAM нҠёлһңм§ҖмҠӨн„° нҳјн•© нҸ¬н•Ё)лҘј лӢ¬м„ұн• мҲҳ мһҲлӢӨкі л§җн–ҲмҠөлӢҲлӢӨ. к·ёлҹ¬лӮҳ м„ұлҠҘкіј м „л Ҙ мҶҢ비мқҳ мӢӨм ң мЎ°н•©мқҙ мӮјм„ұм—җ м–ҙл–»кІҢ мһ‘мҡ©н• м§ҖлҠ” л‘җкі лҙҗм•ј н•©лӢҲлӢӨ.

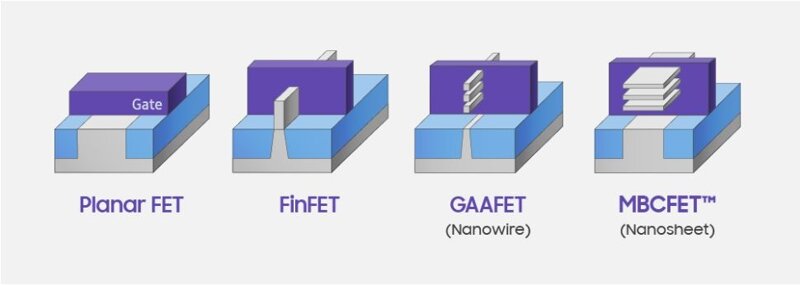

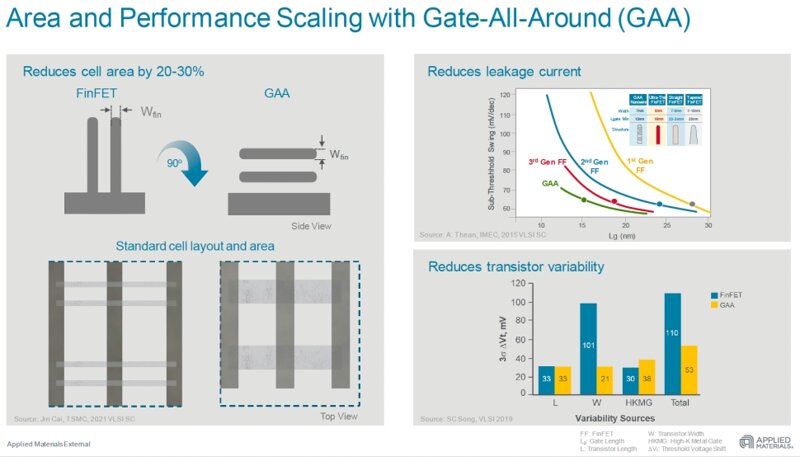

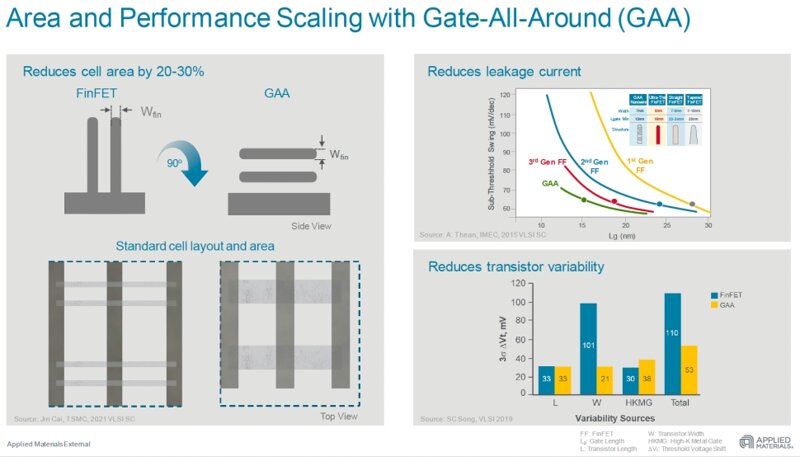

мқҙлЎ м ҒмңјлЎң GAAFETлҠ” нҳ„мһ¬ мӮ¬мҡ©лҗҳлҠ” FinFETмҷҖ 비көҗн• л•Ң м—¬лҹ¬ к°Җм§Җ мһҘм җмқҙ мһҲмҠөлӢҲлӢӨ. GAA нҠёлһңм§ҖмҠӨн„°м—җм„ң мұ„л„җмқҖ мҲҳнҸүмқҙкі кІҢмқҙнҠёлЎң л‘ҳлҹ¬мӢём—¬ мһҲмҠөлӢҲлӢӨ. GAA мұ„л„җмқҖ м—җн”јнғқмӢң л°Ҹ м„ нғқм Ғ мһ¬лЈҢ м ңкұ°лҘј мӮ¬мҡ©н•ҳм—¬ нҳ•м„ұлҗҳлҜҖлЎң м„Өкі„мһҗлҠ” нҠёлһңм§ҖмҠӨн„° мұ„л„җмқҳ л„Ҳ비лҘј мЎ°м •н•ҳм—¬ мқҙлҘј м •л°Җн•ҳкІҢ мЎ°м •н• мҲҳ мһҲмҠөлӢҲлӢӨ. лҚ” л„“мқҖ мұ„л„җмқ„ нҶөн•ҙ кі м„ұлҠҘмқ„ м–»кі лҚ” мўҒмқҖ мұ„л„җмқ„ нҶөн•ҙ м Җм „л Ҙмқ„ м–»мҠөлӢҲлӢӨ. мқҙлҹ¬н•ң м •л°ҖлҸ„лҠ” нҠёлһңм§ҖмҠӨн„° лҲ„м„Ө м „лҘҳ(мҰү, м „л Ҙ мҶҢ비 к°җмҶҢ)мҷҖ нҠёлһңм§ҖмҠӨн„° м„ұлҠҘ ліҖлҸҷм„ұ(лӘЁл“ кІғмқҙ мһҳ мһ‘лҸҷн•ңлӢӨкі к°Җм •)мқ„ нҒ¬кІҢ к°җмҶҢмӢңнӮӨл©°, мқҙлҠ” лҚ” л№ лҘё мҲҳмңЁ, м¶ңмӢң мӢңк°„ л°Ҹ к°ңм„ лҗң мҲҳмңЁмқ„ мқҳлҜён•©лӢҲлӢӨ. лҳҗн•ң Applied Materials мқҳ мөңк·ј л°ңн‘ңм—җ л”°лҘҙл©ҙ GAAFETлҠ” м „м§Җ л©ҙм Ғмқ„ 20%~30% мӨ„мқј мҲҳ мһҲлӢӨкі м•ҪмҶҚн–ҲмҠөлӢҲлӢӨ.

Appliedм—җ лҢҖн•ҙ л§җн•ҳл©ҙм„ң мөңк·ј GAA нҠёлһңм§ҖмҠӨн„° м ңмЎ°мқҳ мЈјмҡ” кіјм ңмқё мӮ¬мҡ© к°ҖлҠҘн•ң мһ‘мқҖ кіөк°„м—җм„ң мұ„л„җ мЈјмң„м—җ лӢӨмёө кІҢмқҙнҠё мӮ°нҷ”л¬ј л°Ҹ кёҲмҶҚ кІҢмқҙнҠё мҠӨнғқмқ„ мҰқм°©н•ҙм•ј н•ҳлҠ” н•„мҡ”м„ұмқ„ н•ҙкІ°н•ҳкё° мң„н•ң кі м§„кіө IMS(нҶөн•© мһ¬лЈҢ мҶ”лЈЁм…ҳ) мӢңмҠӨн…ңм—җ лҢҖн•ҙ м„ӨлӘ…н–ҲмҠөлӢҲлӢӨ. Applied Materialsмқҳ мІ« лІҲм§ё мғҲлЎңмҡҙ IMS лҸ„кө¬лҠ” нҶөн•© мӣҗмһҗмёө мҰқм°©(ALD), м—ҙ, н”ҢлқјмҰҲл§Ҳ мІҳлҰ¬ л°Ҹ кі„мёЎ лӢЁкі„лҘј мӮ¬мҡ©н•ҳм—¬ 1.5мҳ№мҠӨнҠёлЎ¬ лҚ” м–ҮмқҖ кІҢмқҙнҠё мӮ°нҷ”л¬јмқ„ мҰқм°©н• мҲҳ мһҲмҠөлӢҲлӢӨ. кёҲмҶҚ кІҢмқҙнҠё IMSлҠ” мҢҚк·№мһҗ м—”м§ҖлӢҲм–ҙл§Ғкіј лӢӨм–‘н•ң ALD лӢЁкі„лҘј нҶөн•©н•©лӢҲлӢӨ.

мҙҲкё° 3nmкёү м ңмЎ° кё°мҲ мқё мӮјм„ұмқҳ 3GAEлҠ” мЈјлЎң мӮјм„ұ LSI(мӮјм„ұ 칩 к°ңл°ң л¶Җл¬ё)мҷҖ SFмқҳ лӢӨлҘё м•ҢнҢҢ кі к°қ мӨ‘ н•ңл‘җ лӘ…мқҙ мӮ¬мҡ©н• кІғмһ…лӢҲлӢӨ. мӮјм„ұмқҳ LSIмҷҖ SFмқҳ лӢӨлҘё мҙҲкё° кі к°қмқҖ 칩мқ„ л§Өмҡ° лҢҖлҹүмңјлЎң мғқмӮ°н•ҳлҠ” кІҪн–Ҙмқҙ мһҲлӢӨлҠ” м җмқ„ м—јл‘җм—җ л‘җкі 3GAE кё°мҲ мқҙ н•ҙлӢ№ м ңн’Ҳмқҳ мҲҳмңЁкіј м„ұлҠҘмқҙ кё°лҢҖм№ҳлҘј 충мЎұн•ңлӢӨкі к°Җм •н• л•Ң лӢӨмҶҢ л„җлҰ¬ мӮ¬мҡ©лҗ кІғмңјлЎң мҳҲмғҒн•©лӢҲлӢӨ.В

мҷ„м „нһҲ мғҲлЎңмҡҙ нҠёлһңм§ҖмҠӨн„° кө¬мЎ°лЎң м „нҷҳн•ҳлҠ” кІғмқҖ мҷ„м „нһҲ мғҲлЎңмҡҙ лҸ„кө¬лҝҗл§Ң м•„лӢҲлқј мҷ„м „нһҲ мғҲлЎңмҡҙ м ңмЎ° кіөм •мқ„ нҸ¬н•Ён•ҳкё° л•Ңл¬ём—җ мқјл°ҳм ҒмңјлЎң мң„н—ҳн•©лӢҲлӢӨ. лӢӨлҘё кіјм ңлҠ” мғҲлЎңмҡҙ л°°м№ҳ л°©лІ•лЎ , нҸүл©ҙлҸ„ к·ңм№ҷ л°Ҹ лӘЁл“ мғҲлЎңмҡҙ л…ёл“ңм—җ мқҳн•ҙ лҸ„мһ…лҗҳкі мғҲлЎңмҡҙ EDA(м „мһҗ м„Өкі„ мһҗлҸҷнҷ”) мҶҢн”„нҠёмӣЁм–ҙлЎң н•ҙкІ°лҗҳлҠ” лқјмҡ°нҢ… к·ңм№ҷмһ…лӢҲлӢӨ. л§Ҳм§Җл§үмңјлЎң 칩 м„Өкі„мһҗлҠ” 비мҡ©мқҙ л§Һмқҙ л“ңлҠ” мҷ„м „нһҲ мғҲлЎңмҡҙ IPлҘј к°ңл°ңн•ҙм•ј н•©лӢҲлӢӨ.

Bector

Bector